# Infrared Data Association RECOMMENDED SERIAL INTERFACE FOR TRANSCEIVER CONTROL

Version 1.0a

March 29, 2000

1

# **Author:**

Franco Iacobelli (National Semiconductor Corporation)

# **Significant Contributors:**

John Petrilla, Takashi Hidai (Agilent Technologies Inc.) Bryn Owen, Patrick Kam (IBM Corporation) Ray Chock (Calibre Inc.)

# Revision:

March 8, 2000 Table 3-1 Add Rohm to the manufacturers table with ID number OAh.

### INFRARED DATA ASSOCIATION (IrDA) - NOTICE TO THE TRADE -

### SUMMARY:

Following is the notice of conditions and understandings upon which this document is made available to members and non-members of the Infrared Data Association.

- Availability of Publications, Updates and Notices

- Full Copyright Claims Must be Honored

- Controlled Distribution Privileges for IrDA Members Only

- Trademarks of IrDA Prohibitions and Authorized Use

- No Representation of Third Party Rights

- Limitation of Liability

- Disclaimer of Warranty

- Product Testing for IrDA Specification Conformance

### IrDA PUBLICATIONS and UPDATES:

IrDA publications, including notifications, updates, and revisions, are accessed electronically by IrDA members in good standing during the course of each year as a benefit of annual IrDA membership. Electronic copies are available to the public on the IrDA web site located at irda.org. Requests for publications, membership applications or more information should be addressed to: Infrared Data Association, P.O. Box 3883, Walnut Creek, California, U.S.A. 94598; or e-mail address: info@irda.org; or by calling (925) 943-6546 or faxing requests to (925) 943-5600.

### **COPYRIGHT**:

- 1. Prohibitions: IrDA claims copyright in all IrDA publications. Any unauthorized reproduction, distribution, display or modification, in whole or in part, is strictly prohibited.

- 2. Authorized Use: Any authorized use of IrDA publications (in whole or in part) is under NONEXCLUSIVE USE LICENSE ONLY. No rights to sublicense, assign or transfer the license are granted and any attempt to do so is void.

### TRADEMARKS:

- 1. Prohibitions: IrDA claims exclusive rights in its trade names, trademarks, service marks, collective membership marks and feature trademark marks (hereinafter collectively "trademarks"), including but not limited to the following trademarks: INFRARED DATA ASSOCIATION (wordmark alone and with IR logo), IrDA (acronym mark alone and with IR logo), IR logo and MEMBER IrDA (wordmark alone and with IR logo). Any unauthorized use of IrDA trademarks is strictly prohibited.

- 2. Authorized Use: Any authorized use of an IrDA collective membership mark or feature trademark is by NONEXCLUSIVE USE LICENSE ONLY. No rights to sublicense, assign or transfer the license are granted and any attempt to do so is void.

### NO REPRESENTATION of THIRD PARTY RIGHTS:

IrDA makes no representation or warranty whatsoever with regard to IrDA member or third party ownership, licensing or infringement/non-infringement of intellectual property rights. Each recipient of IrDA publications, whether or not an IrDA member, should seek the independent advice of legal counsel with regard to any possible violation of third party rights arising out of the use, attempted use, reproduction, distribution or public display of IrDA publications.

IrDA assumes no obligation or responsibility whatsoever to advise its members or non-members who receive or are about to receive IrDA publications of the chance of infringement or violation of any right of an IrDA member or third party arising out of the use, attempted use, reproduction, distribution or display of IrDA publications.

### LIMITATION of LIABILITY:

BY ANY ACTUAL OR ATTEMPTED USE, REPRODUCTION, DISTRIBUTION OR PUBLIC DISPLAY OF ANY IrDA PUBLICATION, ANY PARTICIPANT IN SUCH REAL OR ATTEMPTED ACTS, WHETHER OR NOT A MEMBER OF IrDA, AGREES TO ASSUME ANY AND ALL RISK ASSOCIATED WITH SUCH ACTS, INCLUDING BUT NOT LIMITED TO LOST PROFITS, LOST SAVINGS, OR OTHER CONSEQUENTIAL, SPECIAL, INCIDENTAL OR PUNITIVE DAMAGES. IrDA SHALL HAVE NO LIABILITY WHATSOEVER FOR SUCH ACTS NOR FOR THE CONTENT, ACCURACY OR LEVEL OF ISSUE OF AN IrDA PUBLICATION.

### **DISCLAIMER of WARRANTY:**

All IrDA publications are provided "AS IS" and without warranty of any kind. IrDA (and each of its members, wholly and collectively, hereinafter "IrDA") EXPRESSLY DISCLAIM ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE AND WARRANTY OF NON-INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS.

Irda does not warrant that its publications will meet your requirements or that any use of a publication will be un-interrupted or error free, or that defects will be corrected. Furthermore, Irda does not warrant or make any representations regarding use or the results or the use of Irda publications in terms of their correctness, accuracy, reliability, or otherwise. No oral or written publication or advice of a representative (or member) of Irda Shall Create a warranty or in any way increase the scope of this warranty.

### **LIMITED MEDIA WARRANTY:**

IrDA warrants ONLY the media upon which any publication is recorded to be free from defects in materials and workmanship under normal use for a period of ninety (90) days from the date of distribution as evidenced by the distribution records of IrDA. IrDA's entire liability and recipient's exclusive remedy will be replacement of the media not meeting this limited warranty and which is returned to IrDA. IrDA shall have no responsibility to replace media damaged by accident, abuse or misapplication. ANY IMPLIED WARRANTIES ON THE MEDIA, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, ARE LIMITED IN DURATION TO NINETY (90) DAYS FROM THE DATE OF DELIVERY. THIS WARRANTY GIVES YOU SPECIFIC LEGAL RIGHTS, AND YOU MAY ALSO HAVE OTHER RIGHTS WHICH VARY FROM PLACE TO PLACE.

# **COMPLIANCE and GENERAL:**

Membership in IrDA or use of IrDA publications does NOT constitute IrDA compliance. It is the sole responsibility of each manufacturer, whether or not an IrDA member, to obtain product compliance in accordance with IrDA Specifications.

All rights, prohibitions of right, agreements and terms and conditions regarding use of IrDA publications and IrDA rules for compliance of products are governed by the laws and regulations of the United States. However, each manufacturer is solely responsible for compliance with the import/export laws of the countries in which they conduct business. The information contained in this document is provided as is and is subject to change without notice.

### 1.1 OVERVIEW

This document describes a simple serial interface that allows an infrared controller to communicate with one or more infrared transceivers. This interface requires three signals: a clock line that is used for timing, and two unidirectional lines multiplexed with the transmitter (write) and receiver (read) infrared signal lines. The main features of the serial interface are listed below.

- Message Based

- Low Power Consumption

- High Speed

- Simple Protocol

- Bus protocol implemented in hardware or in software through bit banging.

- Read and write capability

- Open Architecture (not patented)

- Easily Expandable

### 1.2 BASIC CONFIGURATIONS

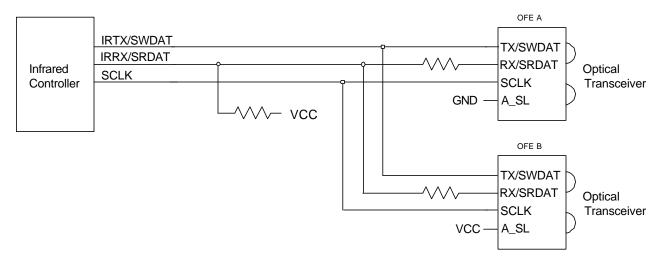

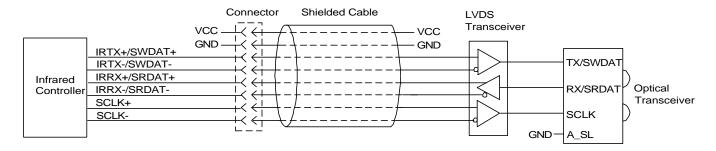

There are two basic system configurations using the serial interface. The first one is found in portable computers and most embedded systems. In this case two optical transceivers are typically used; one in the front and one in the rear of the system's chassis. Furthermore, the infrared controller and transceivers are in close proximity of one another. The interconnections are usually implemented with single ended signals since their contribution to EMI is minimal. Handling multiple optical transceivers is easily accomplished by assigning them different addresses. The second configuration exists typically in desktop systems. In this case only one transceiver is required. The transceiver is usually mounted on a tiny PC board and communicates with the infrared controller through a shielded cable approximately 1.5 m long. This PC board and cable assembly is commonly referred to as Infrared Dongle. Currently existing Dongles use single ended signaling. However, due to the inherent EMI problems of this arrangement, there is a strong incentive in future Dongles to use differential signaling.

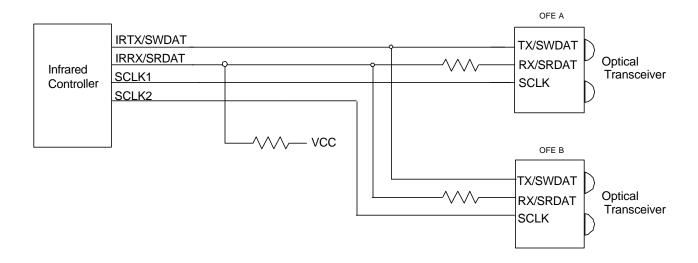

Figures 1-1 and 1-2 below show two typical transceiver configurations.

Figure 1-1. Interface to Two Infrared Transceivers.

The data lines are multiplexed with the transmitter and receiver signals and a different address for each transceiver can be selected. The pullup resistor on the IRRX/SRDAT line is used to prevent spurious low-going transitions during the time in which both transceivers are disabled. When no infrared communication is in progress and the serial interface is

idle, the IRTX/SWDAT line is kept low and IRRX/SRDAT is kept high.

Figure 1-2. Infrared Dongle with Differential Signaling.

### 1.3 FUNCTIONAL DESCRIPTION

The serial interface is designed to interconnect two or more devices. One of the devices is always in control of the serial interface and is responsible for starting every transaction. This device functions as the bus master and is always the infrared controller. The infrared transceivers act as bus slaves and only respond to transactions initiated by the master. A bus transaction is made up of one or two phases. The first phase is the Command Phase and is present in every transaction. The second phase is the Response Phase and is present only in those transactions in which data must be returned from the slave. If the operation involves a data transfer from the slave, there will be a Response Phase following the Command Phase in which the slave will output the data.

The start bit of the slave response, if present, must occur 4 clock cycles after the last bit of the Command Phase, as shown in figures 1-8 and 1-9, otherwise it is assumed that there will be no response. The master must always complete the transaction normally. More precisely, it must not stop the clock and terminate the transaction earlier if the slave does not respond.

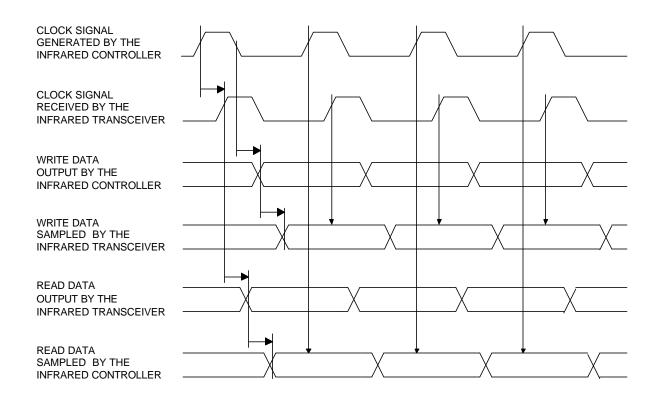

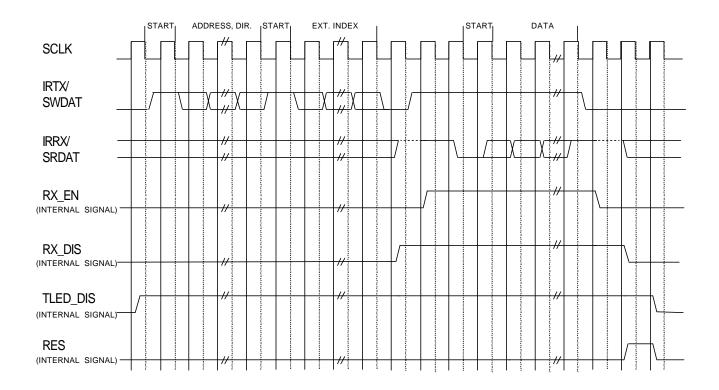

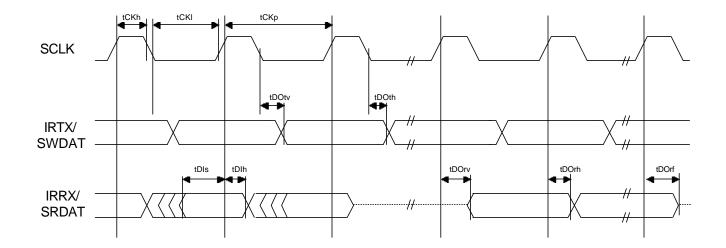

The SCLK line is always driven by the master and is used to clock the data being written to or read from the slave. This line is driven by a totem-pole output buffer. The **SCLK line is always stopped** when the serial interface is idle to minimize power consumption and to avoid any interference with the analog circuitry inside the slave. There are no gaps between the bytes in either the Command or Response Phase. Each byte of data in both Command and Response Phases is preceded by one start bit. Data is always transferred in **Little Endian** order (least significant bit first). Input data is sampled on the rising edge of SCLK. Output data from the controller is clocked by SCLK falling edge. Output data from the slave is clocked by SCLK rising edge. This makes the interface signaling less sensitive to timing skews. Figure 1-3 shows the interface timing including the data sampling points.

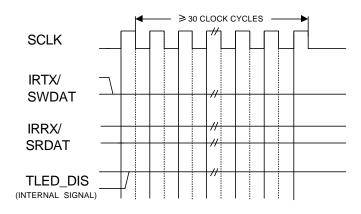

The data to be written to the slave is carried on the IRTX/SWDAT line. When the control interface is idle, this line carries the infrared data signal used to drive the transmitter LED. When the first low-to-high transition on SCLK is detected at the beginning of the command sequence, the slave will disable the transmitter LED. The infrared controller then outputs the command string on the IRTX/SWDAT line. On the last SCLK cycle of the command sequence the slave re-enables the transmitter LED and normal infrared transmission can resume. No transition on SCLK must occur until the next command sequence, otherwise the slave will disable the transmitter LED again. Read data is carried on the IRRX/SRDAT line. The slave disables the internal signal from the receiver photo diode during the response phase of a read transaction. The addressed slave will output the read data on the IRRX/SRDAT line regardless of the setting of the Receiver Output Enable bit in the Mode Selection register 0. Non addressed slaves will tri-state the IRRX/SRDAT line. When the transceiver is powered up, the IRTX/SWDAT line should be kept low and SCLK should be cycled at least 30 times by the infrared controller before the first command is issued on the IRTX/SWDAT line. This guarantees that the transceiver interface circuitry will properly initialize and be ready to receive commands from the controller (note 1). In case of a multiple transceiver configuration, only one transceiver should have the receiver output enabled. If these transceivers are connected to the infrared controller via short traces (like in a notebook computer), a series resistor (approx. 200 ohms) should be placed on the receiver output from each transceiver to prevent large currents in case a conflict occurs due to a programming error.

**Note 1:** Since there is no reset line, the serial interface can be initialized by implementing a self-resetting interface state machine in the transceiver. This machine must be guaranteed to

transition to the idle state by cycling the SCLK line at least 30 times while keeping IRTX low. It is only from the idle state that the transceiver state machine can correctly accept a command from the infrared controller.

Figures 1-4 to 1-9 show the waveforms for the various serial interface operations.

Figure 1-3. Serial Interface Timing.

This figure shows the signal delays due to the cable as well as the data sampling points for both the infrared controller and transceiver.

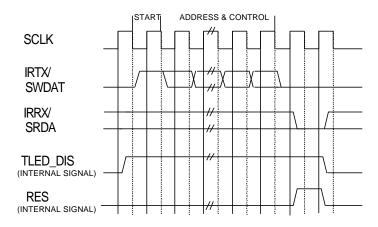

Figure 1-4. Initial Reset Timing

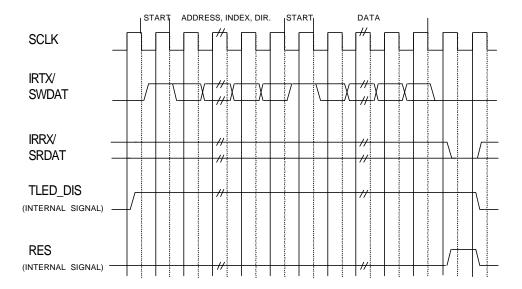

Figure 1-5. Special Command Waveform

Figure 1-6. Write Data Waveform.

Note 2: If the APEN bit in control register 0 is set to 1, the internal signal from the receiver photo diode is disconnected and the IRRX/SRDAT line from the addressed transceiver is pulsed low for one clock cycle at the end of a write or special command. No pulse is generated if a broadcast address is used.

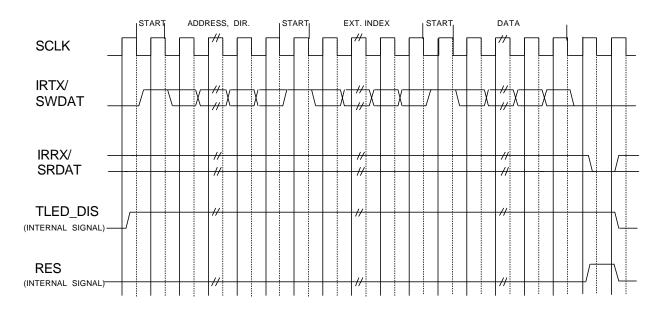

Figure 1-7. Write Data Waveform with Extended Index.

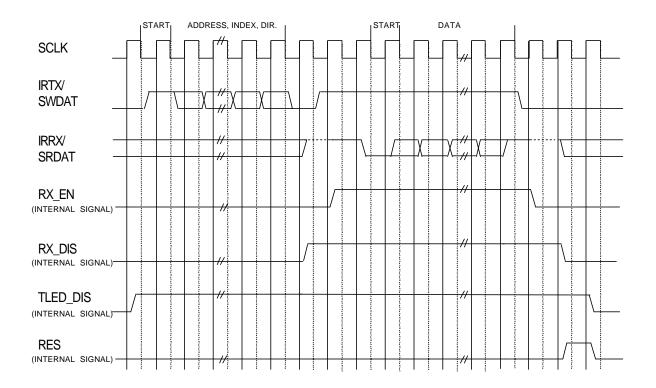

Figure 1-8. Read Data Waveform.

Figure 1-9. Read Data Waveform with Extended Index.

Note 3: During a read transaction the infrared controller sets the IRTX/SWDAT line low for one clock cycle after sending the address and index byte (or bytes). It will then set it high and low again three clock cycles before the end of the transaction.

It is strongly recommended that optical transceivers monitor this line instead of counting clock cycles in order to detect the end of the read transaction.

This will always guarantee correct operation in case two or more transceivers from different manufacturers are sharing the serial interface.

# 2.0 BUS PROTOCOL

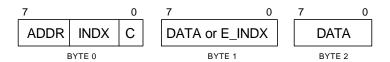

A set of commands is provided to handle the various transactions between the master and each of the slaves. The set is fully expandable to handle future requirements. The general command format is shown in figure 2-1. Data is transferred in little endian order, bit 0 of byte 0 is the first bit transferred, bit 7 of byte 2 is the last.

Figure 2-1. General Command Format.

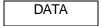

The first byte, common to all transactions, contains the address of the slave to be accessed and two control fields. The first control field is the INDX field. It determines whether the transaction is a Special Transaction or a Data Transaction. The second control field (C field) consists of only one bit and either determines the data transfer direction or it further qualifies a special transaction. The second byte is present in read and write transactions.

It contains either the data being transferred between master and slave, or the 'extended' register index. The third byte contains the data being transferred and it is only present in transactions using the extended index. A slave ignores invalid commands as well as commands specifying a register that is not implemented. Each slave responds to one or more addresses. A slave should provide one or more strap pins to select its address.

Tables 2-1 and 2-2 show the encoding for the address and INDX fields in the first command byte.

**Table 2-1. Device Addressing**

| ADDR[2-0]    | Description                         |

|--------------|-------------------------------------|

| 000 to 101   | 6 Assignable Transceiver Addresses. |

| 110          | Reserved                            |

| 111 (Note 1) | Broadcast Address                   |

**Note 1:** A broadcast address cannot be specified for a read transaction.

A slave must ignore any read transaction with a broadcast address.

Table 2-2. Index Field and C Bit Encodings

| INDX[3-0]    | C Bit      | Description                                       |

|--------------|------------|---------------------------------------------------|

| 0000 to 1011 | X (Note 2) | 12 Assignable Register Indexes                    |

| 1100 to 1101 | 0          | Reserved for Additional Special Commands          |

| 1100         | 0          | Vendor Specific Special Command                   |

| 1100         | 1          | Vendor Specific Special Command                   |

| 1101         | 1          | Reset Transceiver to Default State                |

| 1110         | 1          | Reset AGC and Select Primary Receiver Sensitivity |

| 1111         | X (Note 2) | Escape Code for Extended Indexing                 |

Note 2: The C bit value determines the transfer direction in all register access transactions.

C = 1: write transaction. C = 0: read transaction.

### **Special Transactions**

Special transactions are only one byte long and are designed to control various non-data-transfer functions in the slave. Only two special transactions are currently defined. The first one is used to reset the slave's internal registers to their default state. The second one is used to reset the AGC and to select the primary receiver sensitivity at the end of a transmitted or received frame. Their formats are shown below.

Reset Slave's Internal Registers to Default State

| ADDR[2:0] | 1 | 1 | 0 | 1 | 1 |

|-----------|---|---|---|---|---|

|           |   |   |   |   |   |

Reset AGC and Select Primary Receiver Sensitivity

| ADDR[2:0] | 1 | 1 | 1 | 0 | 1 |

|-----------|---|---|---|---|---|

|           |   |   |   |   |   |

### Write Data Transactions

These transactions are always required and are used to write data into the slave to select the slave's operational mode. Only the command phase is needed.

### Command formats

| ADDR[2:0] | INDX[3-0] |   |   |   | 1 | DATA        |      |

|-----------|-----------|---|---|---|---|-------------|------|

|           |           |   |   |   |   |             |      |

| ADDR[2:0] | 1         | 1 | 1 | 1 | 1 | E_INDX[7-0] | DATA |

- The ADDR field represents the slave address.

- The INDX and E\_INDX fields indicate the slave's register to be written into.

- The DATA field contains the data to be written into the slave to select the operational mode.

**Note:** At least two distinct addresses should be supported since some notebooks use two transceivers, one in the front and one in back. This allows both transceivers to be directly attached to the serial bus.

### **Read Data Transactions**

These transactions are implemented by the slaves in order to support Plug-n-Play or to report the currently selected mode. The data returned by a read transaction may include the slave's operational capabilities and other relevant information. Both command phase and response phase are always present in a read transaction.

# Command phase formats

| ADDR[2:0] | INDX[3:0] |   |   |   | 0 |             |

|-----------|-----------|---|---|---|---|-------------|

|           |           |   |   |   |   |             |

| ADDR[2:0] | 1         | 1 | 1 | 1 | 0 | E_INDX[7:0] |

## Slave Response format

- The ADDR field represents the slave address.

- The INDX and E\_INDX fields indicate the slave's register whose data is to be returned during the response phase.

- The DATA field contains the returned data.

# 3.0 SLAVE INTERNAL REGISTERS

Following is a list of the internal registers that a transceiver may provide. These registers are divided into two groups as described below. Simple transceivers may implement only a subset of these registers. Transceivers do not need to respond to all transaction types or to transactions specifying a register that is not implemented. However, in order to properly operate in multiple transceiver configurations, each transceiver must follow all types of transactions occurring on the serial interface.

### **Main Control Registers**

These registers belong to the first group and are addressed by a 4-bit index field. They are used to control the operational mode of the transceiver. Some bits are used to enable special features and need not be implemented by all transceivers. All the implemented registers must support write accesses. Read accesses are optional.

INDX[3-0]

**Selected Register**

0 Control Register 0. (read/write)

Upon reset, all implemented bits are set to 0.

bit 0 PM SL - Power Mode Select.

0 => low power mode (sleep mode)1 => normal operation power mode

bit 1 RX\_OEN - Receiver Output Enable

0 => IRRX/SRDAT line disabled (tri-stated)

1 => IRRX/SRDAT line enabled

bit 2 TLED EN - Transmitter LED Enable

0 => disabled1 => enabled

bit 3 DM\_EN - CIR/Sharp-IR Demodulation Enable, (Optional).

This bit is optional and may be implemented in transceivers

supporting Consumer-IR and/or Sharp-IR modes.

0 => envelope demodulation disabled1 => envelope demodulation enabled

bit 4 APEN - Acknowledge Pulse Enable, (Optional).

This bit is used to enable the acknowledge pulse.

When it is set to 1 and RX\_OEN is 1 (receiver output enabled), the IRRX/SRDAT line will be pulsed low for one clock cycle upon successful completion of every write command or special command

with individual (non broadcast) transceiver address.

The internal signal from the receiver photo diode is disconnected when

this bit is set to 1.

bit 5 AGCMSK - AGC Mask Enable, (Optional).

When set to 1, the internal signal from the receiver diode is prevented from reaching the AGC circuitry while the transmitter signal is active. This can be used to detect infrared traffic from other sources while a frame

is being transmitted.

bit 6 reserved

bit 7 TAUX EN - Transmitter Auxiliary Output Enable, (Optional).

This bit is used by those transceivers providing an auxiliary output

signal to drive an external transmit LED.

When this bit is set to 1, the auxiliary output signal is enabled.

# 1 Control Register 1. (read/write)

bits 7-0 Infrared Mode Selection.

The value to be written into this register to select a certain infrared mode is the same as the bit offset value of the bit indicating support for that mode. The offset value is calculated from bit 0 of the register at extended index 7.

Upon reset, all implemented bits are set to 0 selecting the SIR mode.

Example encodings are shown below.

0 SIR

1 MIR

2 FIR

3 AppleTalk

4 Air

5 VFIR-16

6 VFIR-TBD

7 VFIR-TBD8 Sharp-IR

32 36 kHz CIR

**Note:** The following control registers are optional. A transceiver manufacturer may choose to implement only a subset of the bits in any of these registers.

However, in order to guarantee software transparency, implemented bits should start from the most significant bit position.

Both Power Level and Receiver Sensitivity settings are binary encoded.

For example, if it is desired to have a total of eight power levels, then each level can be represented as a binary combination of 12, 11 and 10. This combination is then mapped into the control register, starting with the most significant bit.

Control Register 2, bit 7 <= I2

Control Register 2, bit 6 <= I1

Control Register 2, bit 5 <= 10

The least significant five bits are then left unused and return zeros when read.

2 Control Register 2. (read/write)

Upon reset, all implemented bits are set to 1 selecting the standard SIR power level.

bits 7-0 Transmitter Power Level

All 0's => Minimum output power level All 1's => Maximum output power level

3 Control Register 3. (read/write).

This register holds the primary receiver sensitivity.

Writing into this register will select the primary sensitivity.

Upon reset, bit 7 is set to 0 and all the other implemented bits are set to 1 selecting the standard SIR sensitivity.

bits 7-0 Primary Receiver Sensitivity.

All 0's => Highest Sensitivity (lowest threshold)

All 1's => Lowest Sensitivity

4 Control Register 4. (read/write).

This register holds the alternate receiver sensitivity.

Writing into this register will select the alternate sensitivity.

Upon reset, bit 7 is set to 0 and all the other implemented bits are set to 1 selecting the standard SIR sensitivity.

bits 7-0 Alternate Receiver Sensitivity.

All 0's => Highest Sensitivity (lowest threshold)

All 1's => Lowest Sensitivity

5 - 11 These registers are currently reserved.

### **Extended Indexed Registers**

These registers form the second group and are addressed by an 8-bit extended index. They are mainly used for transceiver identification or for vendor specific purposes.

Except for two registers, the implementation of these registers is optional. The two registers with extended index values of 0 and 1 are mandatory since they are used by the infrared software driver to identify the transceiver.

# E\_INDX[7-0] Selected Register

0 Manufacturer's ID

This register returns a value identifying the transceiver's manufacturer.

Currently assigned values are given in table 3-1 below.

Table 3-1. Manufacturer's ID Values .

| Device Manufacturer  | ID Value  |

|----------------------|-----------|

| Agilent Technologies | 01h       |

| IBM                  | 02h       |

| Sharp                | 03h       |

| Vishay-Telefunken    | 04h       |

| Texas Instruments    | 05h       |

| Novalog              | 06h       |

| Unitrode             | 07h       |

| Infineon             | 08h       |

| Calibre              | 09h       |

| Rohm                 | 0Ah       |

| Reserved             | 0Bh - FFh |

| 1 | Device | II ) |

|---|--------|------|

This register returns a value identifying the transceiver. The meanings of the various bits are described below.

bits 5-0 Device type and/or revision level.

This field is manufacturer's specific.

bit 6 Read support for non-extended registers.

This bit is set to 1 if the device supports the reading of all the main control registers.

bit 7 Read support for extended registers.

This bit is set to 1 if the device supports the reading of all the extended indexed registers.

### 2 - 3 Reserved

4 Misc. Capabilities, (read-only)

bits 2-0 Receiver Recovery Time After Transmit.

In the IrLAP document this parameter is referred to as

the Minimum Turnaround Time.

000 0 ms

001

010 011

1xx

bit 7

5

| 001<br>010<br>011<br>100<br>101<br>110        | 0.01 ms 0.05 ms 0.1 ms 0.5 ms 1 ms 5 ms 10 ms                                                       |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------|

|                                               |                                                                                                     |

| bits 3                                        | reserved                                                                                            |

| bits 6-4                                      | Power ON Stabilization Time.                                                                        |

| 00x<br>010<br>011<br>100<br>101<br>110        | reserved 0.5 ms 1 ms 5 ms 10 ms 50 ms reserved                                                      |

| bits 7                                        | reserved                                                                                            |

| Misc. Capabilit                               | ies (read-only)                                                                                     |

| bits 2-0                                      | Receiver Stabilization Time for SIR, MIR, FIR, etc. (Number of additional BOFs or preamble symbols) |

| 000<br>001<br>010<br>011<br>100<br>101<br>110 | 0<br>1<br>2<br>3<br>5<br>12<br>24<br>48                                                             |

| bit 3                                         | reserved                                                                                            |

| bits 6-4                                      | Serial Interface Maximum Speed.                                                                     |

| 000                                           | 100 kHz                                                                                             |

**Note:** In the following registers (with extended index values from 6 to 14) each bit indicates whether a certain capability is supported. The capability is supported if the corresponding bit is set to 1.

| 6 | Misc. Capa | Misc. Capabilities (read-only)                   |  |  |  |

|---|------------|--------------------------------------------------|--|--|--|

|   | bit 0      | Low power mode support.                          |  |  |  |

|   | bit 1      | Support for programmable transmitter power level |  |  |  |

|   | bit 2      | Support for programmable receiver sensitivity    |  |  |  |

500 kHz 1 MHz

4 MHz reserved

reserved

|            | bit 3           | Support for programmable alternate receiver sensitivity            |

|------------|-----------------|--------------------------------------------------------------------|

|            | bit 4           | Support for programmable receiver bandwidth                        |

|            | bit 5           | Programmable CIR or Sharp-IR demodulation support.                 |

|            | bit 6           | Support for CIR traffic monitoring while an IrDA mode is selected. |

|            | bit 7           | Support for automatic wakeup ?                                     |

|            |                 |                                                                    |

| 7          | Supported Infra | ared Modes (read-only)                                             |

|            | bit 0           | SIR                                                                |

|            | bit 1           | MIR                                                                |

|            | bit 2           | FIR                                                                |

|            | bit 3           | AppleTalk                                                          |

|            | bit 4           | Alr                                                                |

|            | bit 5           | VFIR-16                                                            |

|            | bit 6           | VFIR-TBD                                                           |

|            | bit 7           | VFIR-TBD                                                           |

|            |                 |                                                                    |

| 8          | Supported Infra | ared Modes (read-only)                                             |

|            | bit 0           | Sharp-IR                                                           |

|            | bits 7-1        | reserved                                                           |

| _          |                 |                                                                    |

| 9          |                 | Sub-carrier Frequencies (read-only)                                |

|            | bit 0           | reserved                                                           |

|            | bit 1           | CIR base band, low speed (30-57 kHz SCF)                           |

|            | bit 2           | CIR base band, medium speed (400-500 kHz SCF)                      |

|            | bit 3           | CIR base band, high speed (1-2 MHz SCF)                            |

|            | bits 7-4        | reserved                                                           |

| 10         | Cupported CID   | Sub-corrier Fraguencies (road only)                                |

| 10         | bits 0-1        | Sub-carrier Frequencies (read-only)                                |

|            | bits 0-1        | reserved 30 to 35 kHz                                              |

|            | DIIS 2-7        | Each bit indicates one frequency                                   |

|            |                 |                                                                    |

| 11         | Supported CIR   | Sub-carrier Frequencies (read-only)                                |

|            | bits 0-7        | 36 to 43 kHz                                                       |

|            |                 | Each bit indicates one frequency                                   |

| 12         | Supported CIR   | Sub-carrier Frequencies (read-only)                                |

| · <b>-</b> |                 |                                                                    |

|            | bits 0-7        | 44 to 51 kHz                                                       |

13 Supported CIR Sub-carrier Frequencies (read-only)

bits 0-5 52 to 57 kHz

Each bit indicates one frequency

bits 6-7 reserved

14 Supported CIR Sub-carrier Frequencies (read-only)

bit 0 400 kHz bit 1 450 kHz bit 2 480 kHz bits 3-7 reserved

15 - 239 These registers are currently reserved.

240 - 255 These registers are vendor specific.

### 4.0 ELECTRICAL SPECIFICATIONS

Timing specifications are given in table 4-1. Only the timing parameters are specified in this document. Switching thresholds and capacitive loads are not specified since they are outside the scope of this document.

The DC characteristics are provided in the document titled 'Infrared Dongle Interface' available from IrDA.

**Table 4-1. Switching Characteristics**

| Symbol | Parameter                                       | Test Conditions               | Min.   | Max.        | Units |

|--------|-------------------------------------------------|-------------------------------|--------|-------------|-------|

| tCKp   | SCLK Clock Period                               | R.E., SCLK to next R.E., SCLK | 250 ns | ∞<br>(note) |       |

| tCKh   | SCLK Clock High Time                            | R.E., SCLK to F.E. SCLK       | 60     |             | ns    |

| tCKI   | SCLK Clock Low Time                             | F.E., SCLK to R.E. SCLK       | 80     |             | ns    |

| tDOtv  | Output Data Valid (from infrared controller)    | After F.E., SCLK              |        | 40          | ns    |

| tDOth  | Output Data Hold<br>(from infrared controller)  | After F.E., SCLK              | 0      |             | ns    |

| tDOrv  | Output Data Valid (from optical transceiver)    | After R.E., SCLK              |        | 40          | ns    |

| tDOrh  | Output Data Valid<br>(from optical transceiver) | After R.E., SCLK              |        | 40          | ns    |

| tDOrf  | Line Float Delay                                | After R.E., SCLK              |        | 60          | ns    |

| tDIs   | Input Data Setup                                | Before R.E., SCLK             | 10     |             | ns    |

| tDIh   | Input Data Hold                                 | After R.E., SCLK              | 5      |             | ns    |

**Note:** The serial interface must be fully static and must function properly as long as the SCLK clock frequency is within the specified limits. If the clock is stopped in the middle of a transaction and then restarted at

a later time, the transaction must continue from the exact point were it was stopped. The interface logic must not implement any timeout. However, the transmitter LED should be timeout protected to prevent any damage in case of a protocol error.

Figure 4-1. Timing Diagram

### **APPENDIX A**

# Implementation Example

Following is a simple implementation of the *slave side* serial interface. Only write transactions to the main control registers, special commands and reading of the Manufacturer's ID and Device ID registers are supported. Reading of the main control registers as well as read/write accesses to the other extended addressed registers is not supported. This implementation keeps track of read commands and commands using extended indexing so that it can coexist with future implementations.

In order to save logic, this design relies on asynchronous registers. This assumes that the signals from the state machine are glitch free. If this condition is not satisfied, then synchronous registers (e.g. with enable input) must be used instead.

Note: This implementation is not yet tested !

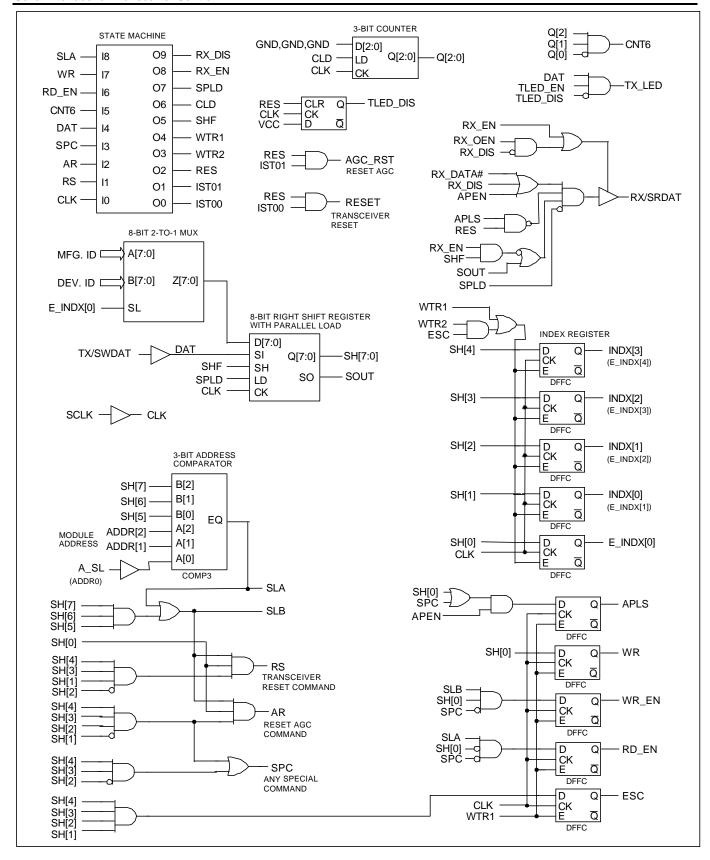

Figure A-1. Serial Interface Circuit Diagram, (Slave Side)

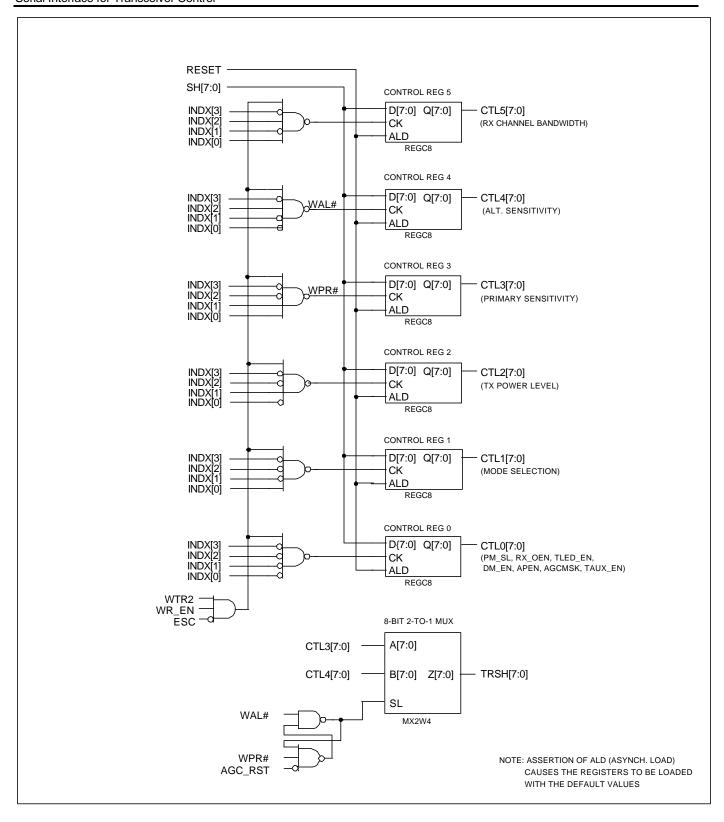

Figure A-2. Transceiver Control Registers

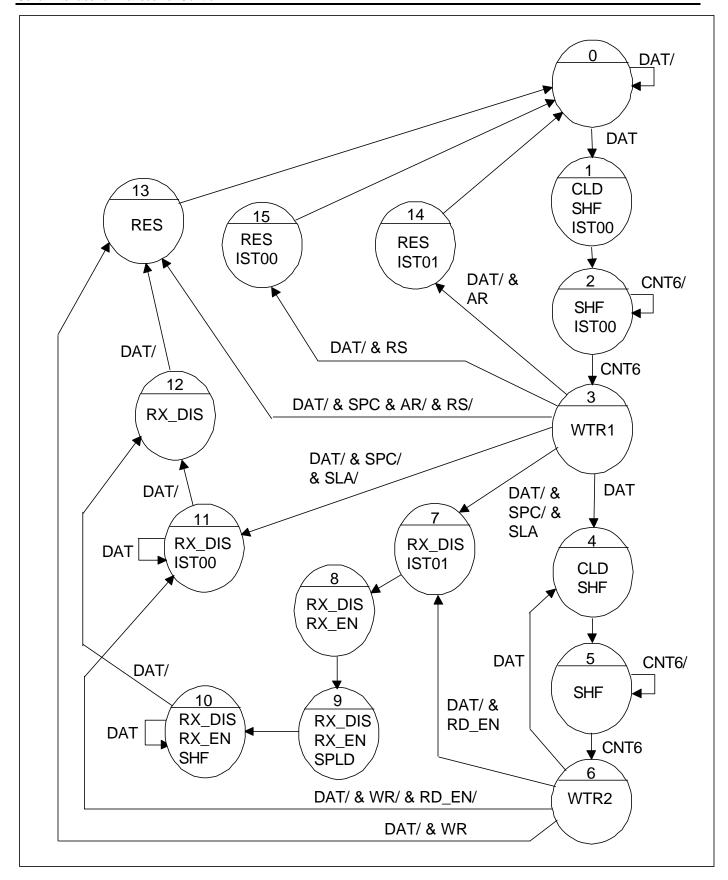

Figure A-3. Serial Interface State Diagram, (Slave Side)

### **APPENDIX B**

# Interconnecting two transceivers with the same address.

The following configuration allows two transceivers having the same fixed address to be used in a system.

This configuration is not part of this specification and should only be considered as an interim solution since it is not expandable and does not support Plug-n-Play.

It is strongly recommended that future transceivers provide support for at least two selectable addresses.

Figure B-1. Interface to Two Infrared Transceivers.

The data lines are multiplexed with the transmitter and receiver signals and separate clocks are used since the transceivers respond to the same address.